フォトニックSRAM(pSRAM)が突破しうる「速度×電力」の限界とは?

「光で計算する」フォトニックコンピューティングは、すでに超高速データ伝送の分野では実用段階に入りつつあります。しかし、実用化を阻む最大の壁として長年指摘されてきたのがメモリ問題です。

光で処理したデータも、最終的には電気のメモリに書き戻す必要があり、そのたびに光↔電気変換による遅延と電力消費が発生します。

こうした根本課題に対し、USC Information Sciences Institute(USC ISI)とウィスコンシン大学マディソン校の研究チームは、世界初となる再生型フォトニックメモリを提唱しました。

この技術は、現代コンピューティングが抱える「処理速度」と「消費電力」の限界を同時に突破する可能性を秘めています。

🧱 なぜ今「光メモリ」が必要なのか?

ボトルネックは“計算”ではなく“データ移動”

近年のコンピュータ性能向上を妨げている最大の要因は、CPUやGPUそのものではなく、データの移動コストです。

- 🔥 金属配線の限界

トランジスタは微細化が進んだ一方、金属配線は抵抗・発熱・信号遅延が深刻化しています。 - 🧠 メモリウォール問題

プロセッサの演算速度に、メモリの読み書きが追いつかない状態が常態化しています。

特にAI分野では、膨大なパラメータやテンソルを頻繁に読み書きするため、消費電力の多くが「計算」ではなく「移動」に使われているのが現実です。

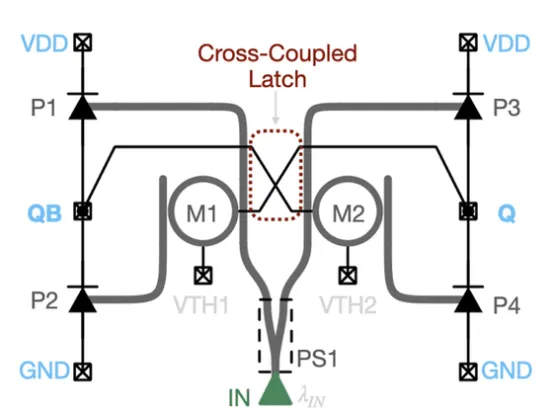

🔑 主役は「再生型フォトニックラッチ」とフォトニックSRAM(pSRAM)

今回の研究で注目されているのは、電子回路におけるSRAMに相当する役割を、光だけで実現しようとする点です。

研究チームはまず、

✅ 1ビットの情報を安定して保持できる「再生型フォトニックラッチ」

を実証しました。

さらにその延長として、**フォトニックSRAM(pSRAM)**へスケール可能な設計を提示しています。

最大の特徴は、特殊材料に頼らず、既存の商用シリコンフォトニクス製造プロセスを前提としている点です。

これは、研究室レベルにとどまらず、量産・実装を見据えた現実的なアプローチであることを意味します。

⚙️ 仕組みをざっくり解説

MRR × フォトダイオード × 交差結合構造

このフォトニックメモリは、以下の要素を組み合わせた独自構造を採用しています。

- 🔄 マイクロリング共振器(MRR)

特定波長の光を共振させ、信号状態を制御 - 📡 フォトダイオード

光信号を電気信号へ変換し、内部状態を安定化 - 🔁 交差結合・差動・再生構造

ノイズに強く、状態が自然に回復する“再生型”設計

この「再生(regenerative)」構造により、電子SRAMと同様に外乱に強く、安定した情報保持が可能になります。

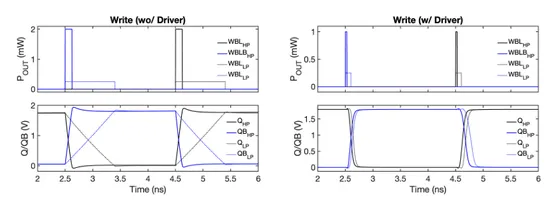

🚀 性能はどれほど凄いのか?

研究チームのシミュレーション結果では、驚異的な数値が示されています。

- ⚡ 読み書き速度:最大40GHz

- 🔋 スイッチングエネルギー:約0.6ピコジュール/ビット

- 🌱 待機時エネルギー:約0.03ピコジュール/ビット

- 📐 ビットセルサイズ:約330×290マイクロメートル

- 🏭 45nm級シリコンフォトニクス商用プロセスを想定

高速かつ省電力でありながら、既存半導体産業と親和性が高い点が非常に重要です。

🏢 想定される主戦場はどこか?

一方で、フォトニック素子は電子回路よりサイズが大きいため、

スマートフォン向けSoCなどにはまだ不向きです。

現実的な適用先としては、次の分野が有力視されています。

- 🖥 データセンター/AIクラスタ

- 🧠 AIアクセラレータ近傍のオンチップメモリ

- 🔬 インメモリコンピューティング(計算と保存の融合)

実際、半導体業界全体でも「光インターコネクト」への移行が加速しており、

**“つなぐ部分は光、次はメモリも光へ”**という流れが見え始めています。

🧩 まとめ:光メモリはAI計算機の設計思想を変えるか?

フォトニックコンピューティング最大の弱点は、

**「メモリだけが電気のまま」**というアンバランスさでした。

今回の研究が示した意義は、

- ✅ 商用プロセス上での再生型フォトニックメモリ実証

- ✅ フォトニックSRAMへ拡張可能な明確な設計指針

- ✅ AI・データセンターの電力効率改善への現実的道筋

という点に集約されます。

今後は、集積密度・周辺回路・熱設計といった実装課題が焦点になりますが、

「光で保存する」という選択肢が、ついに机上の空論を脱し始めました。

✨ 光メモリは、AI時代の計算基盤を根本から変える“静かな革命”になるかもしれません。

📚 参考・出典

- USC Information Sciences Institute(USC ISI)研究ニュース

- ウィスコンシン大学マディソン校 工学部 発表資料

- arXiv論文

Design of Energy-Efficient Cross-coupled Differential Photonic-SRAM (pSRAM) Bitcell for High-Speed On-Chip Photonic Memory and Compute Systems - 国際電子デバイス会議(IEDM 2025)発表予定情報

- 半導体・シリコンフォトニクス分野の業界動向レポート各種